Это Баг? Я все еще не знаю!

Это перевод статьи Is it a bug? I still don’t know!, которая является прологом к написанию автором Alastair M. Robinson своего контроллера SDRAM.

Подводя итог, я выбрал ядро MiST Megadrive/Genesis в качестве своего следующего проекта по портированию на Turbo Chameleon 64 – теоретически простая задача, так как ядро оставляет достаточно логики и оперативной памяти, чтобы просто включить компонент DeMiSTify и поехали.

Кроме…

Ну, ничего не бывает просто, не так ли? Порт отлично работал на Turbo Chameleon 64 V1, отлично работал на DE10-lite и провалился на Chameleon 64 V2.

Проблема упорно не поддавалась корректировке фазовых сдвигов и даже снижению тактовой частоты всего проекта – так что мне нужно было сделать тест – такой, который мог бы работать как в симуляции, так и на реальном оборудовании, – чтобы отследить это.

Контроллер SDRAM в ядре Megadrive имеет несколько портов доступа, и я уже знал, написав простой ROM Megadrive для тестирования, что проблема не проявится, если память не будет использоваться довольно усердно. Поэтому мне нужно было создать сложный шаблон записи/чтения для мультипортов одновременно.

До этого, при тестировании SDRAM, я использовал регистры сдвига с линейной обратной связью, поскольку они генерируют поток значений, которые выглядят довольно случайными, но которые полностью предсказуемы и повторяемы, и, что лучше всего, генерируют каждое значение только один раз в течение всего цикла. Это означает, что я могу писать в ОЗУ, по адресу, сгенерированному LFSR, а затем проверять записанные данные, снова сгенерированные со считанными из ОЗУ.

Однако порты на контроллере различаются как по адресам, так и по шине данных, а это значит, что мне нужно использовать LFSR с разными параметрами. В прошлом настраивал LFSR к нужной базе, используя, как справочник old Xilinx application note, но недавно я написал более универсальный модуль регистра сдвига, который включен в этот и будущие проекты. Я должен признаться, спустился немного в кроличью нору, и вылез с параметризованным модулем, который поддерживает LFSR с шириной до 128 бит. Он также поддерживает сохранение текущего состояния регистра и его восстановление – так что последовательность может быть воспроизведена из любой точки, а не только из начального значения. Так что (не считая опечатки в списках выводов) LFSR, вероятно, не то, о чем мне придется думать снова.

Я настроил модуль porttest, который использует конечный автомат для записи последовательности “случайной” длины со “случайными” значениями на “случайные” адреса, а затем считывает ту же последовательность обратно из оперативной памяти, чтобы проверить ее. Опять же, он параметризован таким образом, чтобы его можно было приспособить к различным портам контроллера SDRAM. Идея состоит в том, чтобы убедиться, что контроллер хорошо работает с использованием одновременно операций чтения и записи, чтобы проверить каждую комбинацию последовательности команд.

Чтобы получить четкое представление о том, что происходит, полезно иметь возможность смоделировать тестовый пример, а для этого требуется модель SDRAM. Micron дает здесь ссылку на хорошую модель verilog своих чипов SDRAM, но, как написано, она несовместима с Verilator. К счастью, György Szombathelyi (который в последние годы проделал огромную работу над ядрами MiST) настроил модель на совместимость с Verilator которая работает в Minimig SDRAM / Cache реализацией, так что с учетом этих изменений и еще нескольких незначительных правок такой, как управление третьим состоянием, я могу запустить свой тестовый пример в симуляции.

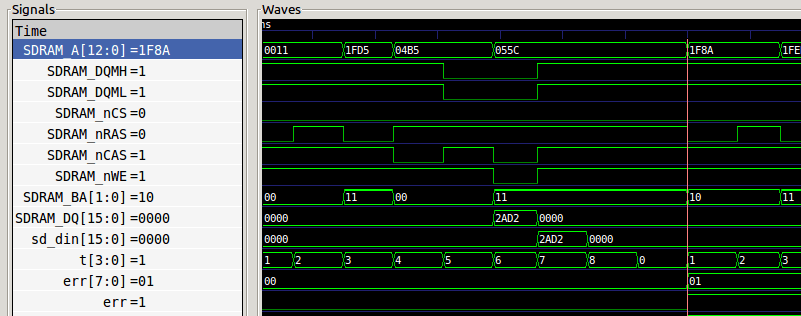

И я вижу ошибки чтения. Вот след первой обнаруженной ошибки:

|

Микросхемы SDRAM, используемые на подопытных платах, содержат четыре банка, которые действуют почти как четыре независимых чипа, разделяющих одну шину. Несмотря на то, что для открытия строки, выдачи команды чтения определенному столбцу и получения данных требуется несколько циклов, при тщательном планировании команд большая часть накладных расходов может перекрываться, что позволяет чрезвычайно эффективно передавать данные. В лучшем случае данные могут передаваться каждый цикл.

Контроллер SDRAM, используемый в этом ядре, обильно использует чередование банков – и это очень хорошо, потому что существует восемь различных подсистем, требующих одновременно доступ к SDRAM!

В приведенной выше последовательности трассировки видно, что сначала открывается для доступа строка в банке 0, затем в банке 3. За этим следует команда чтения в банке 0 (при первом низком уровне CAS), затем команда записи в банк 3 – однако команда чтения в ошибке при моделировании. Причина этого заключается в том, что модель не поддерживает команду записи, выдаваемую в промежутке между получением команды чтения и отправкой данных. Команда записи, по-видимому, предотвращает чтение из-за записи на шину.

Тестовый пример выходит из строя в точно такой же точке на реальном оборудовании, но не на всем реальном оборудовании. В частности, он отлично работает на всех платах, которые я тестировал до сих пор (MiST, Turbo Chameleon 64 V1, DE10-lite и дешевая плата Cyclone IV, купленная на eBay несколько лет назад), и не работает на Turbo Chameleon64 V2 и новейшей плате Cyclone IV от QMTech. Общим для этих двух последних устройств является чип SDRAM – в них установлена Winbond W98G256KH-6. (Хамелеон V1 также оборудован чипом Winbond, но это более ранняя и быстрая версия.)

Поэтому, хотя у меня нет фактических доказательств, на данный момент я считаю, что, как и модель verilog, новый чип Winbond просто не поддерживает этот конкретный шаблон доступа, и переписывание контроллера, чтобы избежать его, устранит проблему, как в симуляции, так и на реальном оборудовании. Я подозреваю – хотя опять же у меня нет доказательств, – что этот шаблон доступа на самом деле вообще недействителен и просто работает на большинстве чипов как причуда реализации. Ни в одной из спецификации, которые я читал до сих пор, не упоминается этот шаблон – хотя, по общему признанию, они тоже не запрещают его, – однако тот факт, что сигнал DQM в команде записи также влияют на последующее чтение, дает намек на то, что это может быть проблематично.

Однако в результате всего этого мне придется иметь разные версии контроллера SDRAM для разных плат, чего я надеялся избежать.

В следующий раз я расскажу о настройке и переписывании контроллера, чтобы избежать этой ловушки.

Адрес для контактов : imax9@narod.ru

Если вам понравились мои работы и вы желаете поддержать сайт - сделайте дотацию.

При копировании статьи – обязательна ссылка на авторство и источник. Без разрешения автора копирование запрещено.

© Максим Ильин 2021г.