Чередование чтения и записи

Предлагаю вам перевод цикла Writing a new SDRAM controller Part 2 автора Alastair M. Robinson.

В прошлый раз я говорил о виде типичного цикла чтения SDRAM и о том, как мы можем улучшить общую пропускную способность, чередуя чтения в разных банках. Тот же принцип применим и к циклам записи.

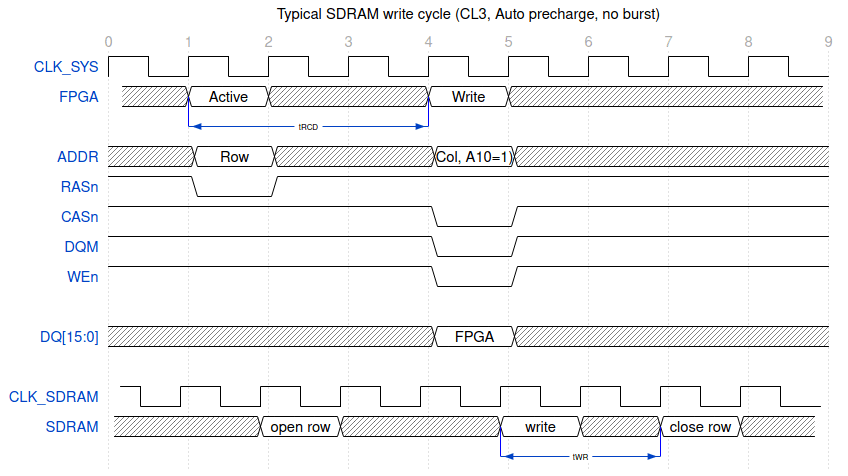

Вот как выглядит типичный цикл записи:

|

Это довольно похоже на чтение; строка открывается таким же образом, активной командой (RASn в лог "0"), затем по истечении tRCD FPGA управляет шиной DQ с записываемыми данными, устанавливаем сигналы DQM и выдает команду записи (CASn и WEn переводим в лог "0"). SDRAM фиксирует данные, записывает их в строку, а затем, по истечении tWR, закрывает строку.

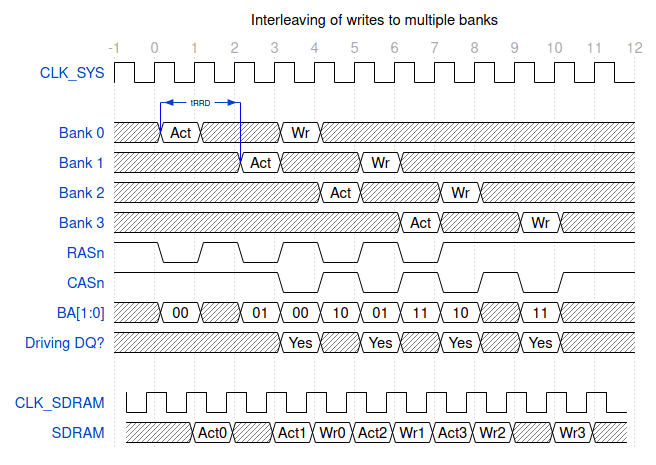

Чередование нескольких команд записи также довольно просто:

|

Мы снова играем в похожую на тетрис игру “заполните каждый пустой слот”, и если у нас есть куча записей спина к спине, мы делаем это довольно хорошо.

И все становится немного запутаннее, когда нам приходится смешивать чтение и запись. Они имеют разный “вид”, поэтому чередуются не так аккуратно. Также очень важно, чтобы мы не закончили тем, что и FPGA, и микросхема SDRAM управляют шиной одновременно.

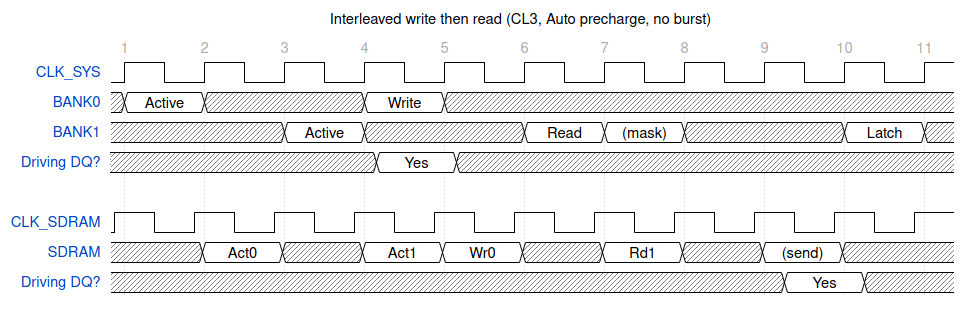

Запись с последующим чтением – это не проблема- все сходится, даже если у нас остается несколько неиспользуемых циклов:

|

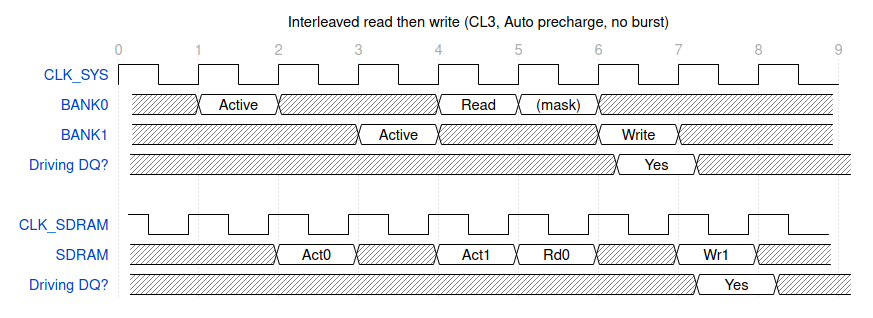

Чтение с последующей записью немного сложнее. Если мы будем следовать стратегии простой упаковки инструкций как можно плотнее, то в конечном итоге получим следующее :

|

Здесь есть две проблемы. Во-первых, хотя этот паттерн отлично работает на большом количестве SDRAM, он не работает в имитационной модели Micron, которую я использовал в разработке, а также не работает на чипе Winbond W9825G6KH в Chameleon64V2.

Другая проблема заключается в том, что из-за того, что у нас FPGA и SDRAM управляют шиной в соседних циклах, мы рискуем столкнуться с конфликтом шин.

Давайте подробнее рассмотрим, как на самом деле чип SDRAM управляет шиной.

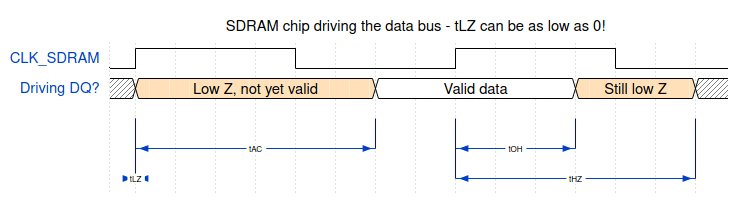

В режиме ожидания оба чипа будут иметь отключенные выходные драйверы, поэтому шина будет в Z состоянии - высокого импеданса. Реагируя на команду чтения, чип SDRAM помещает действительные данные в линию по истечению tAC после тактового фронта, который обычно находится между 5,5 и 6ns. Однако это не означает, что до этого момента шина остается высокоимпедансной. Выходные драйверы SDRAM включаются почти сразу после тактового фронта – tLZ обычно составляет 1ns или меньше – и может быть 0ns. В то время как данные гарантированно остаются действительными только для tOH после тактового фронта, шина остается управляемой до tHZ. Таким образом, существует значительный период по обе стороны от окна действительных данных, где SDRAM управляет шиной.

|

Поэтому мы должны быть очень осторожны при записи на шину в соседних циклах – если мы это сделаем, то она должна быть рассчитана очень тщательно (с учетом фазовых сдвигов между тактовым сигналом и любыми задержками платы), чтобы избежать конфликтов, – а на более высоких скоростях это может оказаться невозможным.

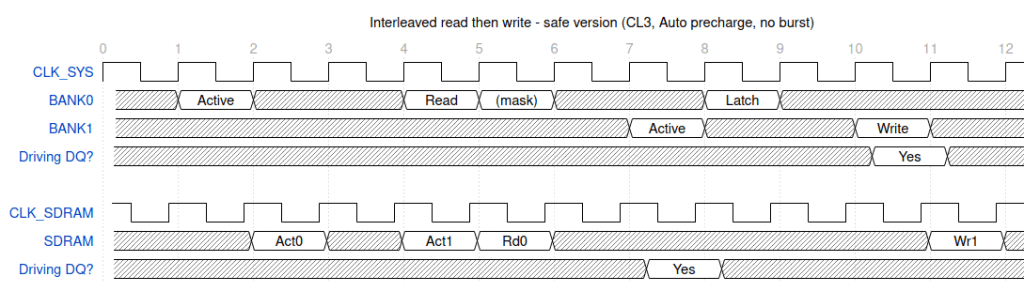

По этой причине контроллер, который я описываю в этой серии, пожертвует некоторой максимальной пропускной способностью во имя безопасности, и когда за чтением последует запись, два потенциальных слота останутся пустыми.

|

(Обратите внимание, что на самом деле я задерживаю запись на один цикл больше, чем это строго необходимо – требования к времени ядра, поддерживаемого этим контроллером, чрезвычайно жесткие, и это помогает поддерживать работу контроллера на всех четных или нечетных циклах.)

В следующий раз я рассмотрю обработку приоритета портов, диспетчеризацию запросов и способы удовлетворения довольно строгих требований к синхронизации тактовой частоты 128 МГц.

Адрес для контактов : imax9@narod.ru

Если вам понравились мои работы и вы желаете поддержать сайт - сделайте дотацию.

При копировании статьи – обязательна ссылка на авторство и источник. Без разрешения автора копирование запрещено.

© Максим Ильин 2021г.